Логические схемы 1. Цифровые логические элементы. Правила ввода логической функции

Читайте также

Любые цифровые микросхемы строятся на основе простейших логических элементов:

Рассмотрим устройство и работу цифровых логических элементов подробнее.

Инвертор

Простейшим логическим элементом является инвертор, который просто изменяет входной сигнал на прямо противоположное значение. Его записывается в следующем виде:

где черта над входным значением и обозначает изменение его на противоположное. То же самое действие можно записать при помощи , приведённой в таблице 1. Так как вход у инвертора только один, то его таблица истинности состоит всего из двух строк.

Таблица 1. Таблица истинности логического элемента инвертора

| In | Out |

|---|---|

| 0 | 1 |

| 1 | 0 |

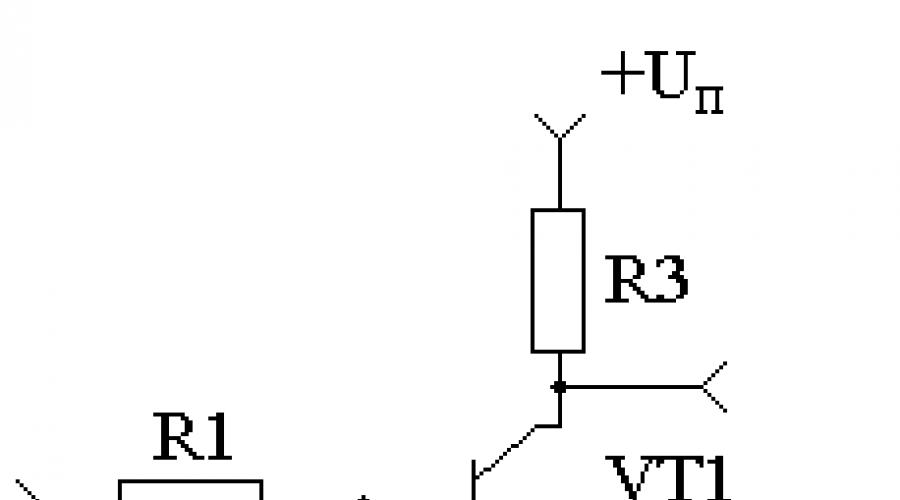

В качестве логического инвертора можно использовать простейший усилитель с транзистором, включенном по (или истоком для полевого транзистора). Принципиальная схема логического элемента инвертора, выполненная на биполярном n-p-n транзисторе, приведена на рисунке 1.

Рисунок 1. Схема простейшего логического инвертора

Микросхемы логических инверторов могут обладать различным временем распространения сигнала и могут работать на различные виды нагрузки. Они могут быть выполнены на одном или на нескольких транзисторах. Наиболее распространены логические элементы, выполненные по ТТЛ, ЭСЛ и КМОП технологиям. Но независимо от схемы логического элемента и её параметров все они осуществляют одну и ту же функцию.

Для того, чтобы особенности включения транзисторов не затеняли выполняемую функцию, были введены специальные обозначения для логических элементов — условно-графические обозначения. инвертора приведено на рисунке 2.

Рисунок 2. Условно-графическое обозначение логического инвертора

Инверторы присутствуют практически во всех сериях цифровых микросхем. В отечественных микросхемах инверторы обозначаются буквами ЛН. Например, в микросхеме 1533ЛН1 содержится 6 инверторов. Иностранные микросхемы для обозначения типа микросхемы используется цифровое обозначение. В качестве примера микросхемы, содержащей инверторы, можно назвать 74ALS04. В названии микросхемы отражается, что она совместима с ТТЛ микросхемами (74), произведена по улучшеной малопотребляющей шоттки технологии (ALS), содержит инверторы (04).

В настоящее время чаще применяются микросхемы поверхностного монтажа (SMD микросхемы), в которых содержится по одному логическому элементу, в частности инвертору. В качестве примера можно назвать микросхему SN74LVC1G04. Микросхема произведена фирмой Texas Instruments (SN), совместима с ТТЛ микросхемами (74) произведена по низковольтовой КМОП технологии (LVC), содержит только один логический элемент (1G), им является инвертор (04).

Для исследования инвертирующего логического элемента можно использовать широкодоступные радиоэлектронные элементы. Так, в качестве генератора входных сигналов можно использовать обычные переключатели или тумблеры. Для исследования таблицы истинности можно даже применить обычный провод, который будем поочередно подключать к источнику питания и ли общему проводу. В качестве логического пробника может быть использована низковольтовая лампочка или светодиод, соединенный последовательно с токоограничивающим . Принципиальная схема исследования логического элемента инвертора, реализованная с помощью этих простейших радиоэлектронных элементов, приведена на рисунке 3.

Рисунок 3. Схема исследования логического инвертора

Схема исследования цифрового логического элемента, приведенная на рисунке 3, позволяет наглядно получить данные для таблицы истинности. Подобное исследование проводится в Более полные характеристики цифрового логического элемента инвертора, такие как время задержки входного сигнала, скорость нарастания и спадания фронтов сигнала на выходе, можно получить при помощи импульсного генератора и осциллографа (желательно двухканального осциллографа).

Логический элемент "И"

Следующим простейшим логическим элементом является схема, реализующая операцию логического умножения "И":

F(x 1 ,x 2) = x 1 ^x 2где символ ^ и обозначает функцию логического умножения. Иногда эта же функция записывается в другом виде:

F(x 1 ,x 2) = x 1 ^x 2 = x 1 ·x 2 = x 1 &x 2 .То же самое действие можно записать при помощи таблицы истинности, приведённой в таблице 2. В формуле, приведенной выше использовано два аргумента. Поэтому логический элемент, выполняющий эту функцию имеет два входа. Он обозначается "2И". Для логического элемента "2И" таблица истинности будет состоять из четырех строк (2 2 = 4) .

Таблица 2. Таблица истинности логического элемента "2И"

| In1 | In2 | Out |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Как видно из приведённой таблицы истинности, активный сигнал на выходе этого логического элемента появляется только тогда, когда и на входе X, и на входе Y будут присутствовать единицы. То есть этот логический элемент действительно реализует операцию "И".

Проще всего понять, как работает логический элемент "2И", при помощи схемы, построенной на идеализированных ключах с электронным управлением, как это показано на рисунке 2. В приведенной принципиальной схеме ток будет протекать только тогда, когда оба ключа будут замкнуты, а, значит, единичный уровень на ее выходе появится только при двух единицах на входе.

Рисунок 4. Принципиальная схема логического элемента "2И"

Условно-графическое изображение схемы, выполняющей логическую функцию "2И", на принципиальных схемах приведено на рисунке 3, и с этого момента схемы, выполняющие функцию “И” будут приводиться именно в таком виде. Это изображение не зависит от конкретной принципиальной схемы устройства, реализующей функцию логического умножения.

Рисунок 5. Условно-графическое изображение логического элемента "2И"

Точно так же описывается и функция логического умножения трёх переменных:

F (x 1 ,x 2 ,x 3)=x 1 ^x 2 ^x 3Её таблица истинности будет содержать уже восемь строк (2 3 = 4). Таблица истинности трёхвходовой схемы логического умножения "3И" приведена в таблице 3, а условно-графическое изображение на рисунке 4. В схеме же логического элемента "3И", построенной по принципу схемы, приведённой на рисунке 2, придётся добавить третий ключ.

Таблица 3. Таблица истинности схемы, выполняющей логическую функцию "3И"

| In1 | In2 | In3 | Out |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Получить подобную таблицу истинности можно при помощи схемы исследования логического элемента "3И", подобной схеме исследования логического инвертора, приведенной на рисунке 3.

Рисунок 6. Условно-графическое обозначение схемы, выполняющей логическую функцию "3И"

Логический элемент "ИЛИ"

Следующим простейшим логическим элементом является схема, реализующая операцию логического сложения "ИЛИ":

F(x 1 ,x 2) = x 1 Vx 2где символ V обозначает функцию логического сложения. Иногда эта же функция записывается в другом виде:

F(x 1 ,x 2) = x 1 Vx 2 = x 1 +x 2 = x 1 |x 2 .То же самое действие можно записать при помощи таблицы истинности, приведённой в таблице 4. В формуле, приведенной выше использовано два аргумента. Поэтому логический элемент, выполняющий эту функцию имеет два входа. Такой элемент обозначается "2ИЛИ". Для элемента "2ИЛИ" таблица истинности будет состоять из четырех строк (2 2 = 4).

Таблица 4. Таблица истинности логического элемента "2ИЛИ"

| In1 | In2 | Out |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Как и в случае, рассмотренном для , воспользуемся для реализации схемы "2ИЛИ" ключами. На этот раз соединим ключи параллельно. Схема, реализующая таблицу истинности 4, приведена на рисунке 5. Как видно из приведённой схемы, уровень логической единицы появится на её выходе, как только будет замкнут любой из ключей, то есть схема реализует таблицу истинности, приведённую в таблице 4.

Рисунок 7. Принципиальная схема логического элемента "2ИЛИ"

Так как функция логического суммирования может быть реализована различными принципиальными схемами, то для обозначения этой функции на принципиальных схемах используется специальный символ "1", как это приведено на рисунке 6.

Рисунок 6. Условно-графическое изображение логического элемента, выполняющего функцию "2ИЛИ"

Дата последнего обновления файла 29.03.2018

Литература:

Со статьей "логические элементы" читают:

Любая логическая схема без памяти полностью описывается таблицей истинности... Для реализации таблицы истинности достаточно рассмотреть только те строки...

http://сайт/digital/SintSxem.php

Декодеры (дешифраторы) позволяют преобразовывать одни виды бинарных кодов в другие. Например...

http://сайт/digital/DC.php

Достаточно часто перед разработчиками цифровой аппаратуры встаёт обратная задача. Требуется преобразовать восьмиричный или десятичный линейный код в...

http://сайт/digital/Coder.php

Мультиплексорами называются устройства, которые позволяют подключать несколько входов к одному выходу...

http://сайт/digital/MS.php

Демультиплексорами называются устройства... Существенным отличием от мультиплексора является...

http://сайт/digital/DMS.php

Бит — это минимальная единица измерения объёма информации, так как она хранит одно из двух значений — 0 (False) или 1 (True). False и True в переводе на русский ложь и истина соответственно. То есть одна битовая ячейка может находиться одновременно лишь в одном состоянии из возможных двух. Напомню, два возможных состояния битовой ячейки равны — 1 и 0.

Есть определённые операции, для манипуляций с битами. Эти операции называются логическими или булевыми операциями, названные в честь одного из математиков — Джорджа Буля (1815-1864), который способствовал развитию этой области науки.

Все эти операции могут быть применены к любому биту, независимо от того, какое он имеет значение — 0(нуль) или 1(единицу). Ниже приведены основные логические операции и примеры их использования.

Логическая операция И (AND)

Обозначение AND: &

Логическая операция И выполняется с двумя битами, назовем их a и b. Результат выполнения логической операции И будет равен 1, если a и b равны 1, а во всех остальных (других) случаях, результат будет равен 0. Смотрим таблицу истинности логической операции and.

| a(бит 1) | b(бит 2) | a(бит 1) & b(бит 2) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Логическая операция ИЛИ (OR)

Обозначение OR: |

Логическая операция ИЛИ выполняется с двумя битами (a и b). Результат выполнения логической операции ИЛИ будет равен 0, если a и b равны 0 (нулю), а во всех остальных (других) случаях, результат равен 1 (единице). Смотрим таблицу истинности логической операции OR.

| a(бит 1) | b(бит 2) | a(бит 1) | b(бит 2) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Логическая операция исключающее ИЛИ (XOR).

Обозначение XOR: ^

Логическая операция исключающее ИЛИ выполняется с двумя битами (a и b). Результат выполнения логической операции XOR будет равен 1 (единице), если один из битов a или b равен 1 (единице), во всех остальных случаях, результат равен 0 (нулю). Смотрим таблицу истинности логической операции исключающее ИЛИ.

| a(бит 1) | b(бит 2) | a(бит 1) ^ b(бит 2) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Логическая операция НЕ (not)

Обозначение NOT: ~

Логическая операция НЕ выполняется с одним битом. Результат выполнения этой логической операции напрямую зависит от состояния бита. Если бит находился в нулевом состоянии, то результат выполнения NOT будет равен единице и наоборот. Смотрим таблицу истинности логической операции НЕ.

| a(бит 1) | ~a(отрицание бита) |

|---|---|

| 0 | 1 |

| 1 | 0 |

Запомните эти 4 логические операции. Используя эти логические операции, мы можем получить любой возможный результат. Подробно об использовании логических операций в С++ читаем .

Назначение сервиса . Онлайн-калькулятор предназначен для построения таблицы истинности для логического выражения .Таблица истинности – таблица содержащая все возможные комбинации входных переменных и соответствующее им значения на выходе.

Таблица истинности содержит 2 n строк, где n – число входных переменных, и n+m – столбцы, где m – выходные переменные.

Инструкция

. При вводе с клавиатуры используйте следующие обозначения:

Например, логическое выражение abc+ab~c+a~bc необходимо ввести так: a*b*c+a*b=c+a=b*c

Для ввода данных в виде логической схемы используйте этот сервис .

Правила ввода логической функции

- Вместо символа v (дизъюнкция, ИЛИ) используйте знак + .

- Перед логической функцией не надо указывать обозначение функции. Например, вместо F(x,y)=(x|y)=(x^y) необходимо ввести просто (x|y)=(x^y) .

- Максимальное количество переменных равно 10 .

Проектирование и анализ логических схем ЭВМ ведётся с помощью специального раздела математики - алгебры логики. В алгебре логики можно выделить три основные логические функции: "НЕ" (отрицание), "И" (конъюнкция), "ИЛИ" (дизъюнкция).

Для создания любого логического устройства необходимо определить зависимость каждой из выходных переменных от действующих входных переменных такая зависимость называется переключательной функцией или функцией алгебры логики.

Функция алгебры логики называется полностью определённой если заданы все 2 n её значения, где n – число выходных переменных.

Если определены не все значения, функция называется частично определённой.

Устройство называется логическим, если его состояние описывается с помощью функции алгебры логики.

Для представления функции алгебры логики используется следующие способы:

- словесное описание – это форма, которая используется на начальном этапе проектирования имеет условное представление.

- описание функции алгебры логики в виде таблицы истинности.

- описание функции алгебры логики в виде алгебраического выражения: используется две алгебраические формы ФАЛ:

а) ДНФ – дизъюнктивная нормальная форма – это логическая сумма элементарных логических произведений. ДНФ получается из таблицы истинности по следующему алгоритму или правилу:

1) в таблице выбираются те строки переменных для которых функция на выходе =1 .

2) для каждой строки переменных записывается логическое произведение; причём переменные =0 записываются с инверсией.

3) полученное произведение логически суммируется.

Fднф= X 1 *Х 2 *Х 3 ∨ Х 1 x 2 Х 3 ∨ Х 1 Х 2 x 3 ∨ Х 1 Х 2 Х 3

ДНФ называется совершенной, если все переменные имеют одинаковый ранг или порядок, т.е. в каждое произведение обязательно должны включаться все переменные в прямом или инверсном виде.

б) КНФ – конъюнктивная нормальна форма – это логическое произведение элементарных логических сумм.

КНФ может быть получена из таблицы истинности по следующему алгоритму:

1) выбираем наборы переменных для которых функция на выходе =0

2) для каждого набора переменных записываем элементарную логическую сумму, причём переменные =1 записываются с инверсией.

3) логически перемножаются полученные суммы.

Fскнф=(X 1 V X 2 V X 3) ∧ (X 1 V X 2 V X 3) ∧ (X 1 V X 2 V X 3) ∧ (X 1 V X 2 V X 3)

КНФ называется совершенной , если все переменные имеют одинаковый ранг.

Рисунок1- Схема логического устройства

Все операции алгебры логики определяются таблицами истинности значений. Таблица истинности определяет результат выполнения операции для всех возможны х логических значений исходных высказываний. Количество вариантов, отражающих результат применения операций, будет зависеть от количества высказываний в логическом выражении. Если число высказываний в логическом выражении N, то таблица истинности будет содержать 2 N строк, так как существует 2 N различных комбинаций возможных значений аргументов.

Операция НЕ - логическое отрицание (инверсия)

Логическая операция НЕ применяется к одному аргументу, в качестве которого может быть и простое, и сложное логическое выражение. Результатом операции НЕ является следующее:- если исходное выражение истинно, то результат его отрицания будет ложным;

- если исходное выражение ложно, то результат его отрицания будет истинным.

не А, Ā, not A, ¬А, !A

Результат операции отрицания НЕ определяется следующей таблицей истинности:

| A | не А |

| 0 | 1 |

| 1 | 0 |

Результат операции отрицания истинен, когда исходное высказывание ложно, и наоборот.

Операция ИЛИ - логическое сложение (дизъюнкция, объединение)

Логическая операция ИЛИ выполняет функцию объединения двух высказываний, в качестве которых может быть и простое, и сложное логическое выражение. Высказывания, являющиеся исходными для логической операции, называют аргументами. Результатом операции ИЛИ является выражение, которое будет истинным тогда и только тогда, когда истинно будет хотя бы одно из исходных выражений.Применяемые обозначения: А или В, А V В, A or B, A||B.

Результат операции ИЛИ определяется следующей таблицей истинности:

Результат операции ИЛИ истинен, когда истинно А, либо истинно В, либо истинно и А и В одновременно, и ложен тогда, когда аргументы А и В - ложны.

Операция И - логическое умножение (конъюнкция)

Логическая операция И выполняет функцию пересечения двух высказываний (аргументов), в качестве которых может быть и простое, и сложное логическое выражение. Результатом операции И является выражение, которое будет истинным тогда и только тогда, когда истинны оба исходных выражения.Применяемые обозначения: А и В, А Λ В, A & B, A and B.

Результат операции И определяется следующей таблицей истинности:

| A | B | А и B |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Результат операции И истинен тогда и только тогда, когда истинны одновременно высказывания А и В, и ложен во всех остальных случаях.

Операция «ЕСЛИ-ТО» - логическое следование (импликация)

Эта операция связывает два простых логических выражения, из которых первое является условием, а второе - следствием из этого условия.Применяемые обозначения:

если А, то В; А влечет В; if A then В; А→ В.

Таблица истинности:

| A | B | А → B |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Результат операции следования (импликации) ложен только тогда, когда предпосылка А истинна, а заключение В (следствие) ложно.

Операция «А тогда и только тогда, когда В» (эквивалентность, равнозначность)

Применяемое обозначение: А ↔ В, А ~ В.Таблица истинности:

| A | B | А↔B |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Операция «Сложение по модулю 2» (XOR, исключающее или, строгая дизъюнкция)

Применяемое обозначение: А XOR В, А ⊕ В.Таблица истинности:

| A | B | А⊕B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Результат операции эквивалентность истинен только тогда, когда А и В одновременно истинны или одновременно ложны.

Приоритет логических операций

- Действия в скобках

- Инверсия

- Конъюнкция (&)

- Дизъюнкция (V), Исключающее ИЛИ (XOR), сумма по модулю 2

- Импликация (→)

- Эквивалентность (↔)

Совершенная дизъюнктивная нормальная форма

Совершенная дизъюнктивная нормальная форма формулы (СДНФ) это равносильная ей формула, представляющая собой дизъюнкцию элементарных конъюнкций, обладающая свойствами:- Каждое логическое слагаемое формулы содержит все переменные, входящие в функцию F(x 1 ,x 2 ,...x n).

- Все логические слагаемые формулы различны.

- Ни одно логическое слагаемое не содержит переменную и её отрицание.

- Ни одно логическое слагаемое формулы не содержит одну и ту же переменную дважды.

Для каждой функции СДНФ и СКНФ определены единственным образом с точностью до перестановки.

Совершенная конъюнктивная нормальная форма

Совершенная конъюнктивная нормальная форма формулы (СКНФ) это равносильная ей формула, представляющая собой конъюнкцию элементарных дизъюнкций, удовлетворяющая свойствам:- Все элементарные дизъюнкции содержат все переменные, входящие в функцию F(x 1 ,x 2 ,...x n).

- Все элементарные дизъюнкции различны.

- Каждая элементарная дизъюнкция содержит переменную один раз.

- Ни одна элементарная дизъюнкция не содержит переменную и её отрицание.

Логические элементы это элементарные цифровые устройства, используемые для обработки информации в цифровой последовательности сигналов высокого - «1» и низкого - «0» уровней, выполняющие логические операции И, ИЛИ, НЕ и различные комбинации этих операций

Первым и самым простым логическим элементом является инвертор, выполняющий логическую операцию НЕ - инверсию или логическое отрицание. На вход подается один сигнал, на выходе противоположный. На вход подается - "0", на выходе - "1" или на вход поступает "1", а на выходе "0".

Так как вход у элемента НЕ только один, то его таблица истинности состоит всего из двух строк.

В роли инвертора можно применять обычный транзисторный усилитель включенный по схеме с общим эмиттером или истоком. Пример такого подключения на биполярном n-p-n транзисторе, показан на рисунке ниже.

В зависимости от схемотехнического исполнения инвертор может обладать различным временем передачи сигнала и может работать на различную нагрузку. Он может быть собран на одном или на нескольких транзисторах, но независимо от схемы все инверторы осуществляют одну и ту же функцию. Поэтому, чтобы особенности включения транзисторов не затеняли выполняемую функцию, используются специальные обозначения для цифровых микросхем. Условно-графическое обозначение инвертора приведено на рисунке.

Инверторы имеются во всех сериях цифровых микросхем. В отечественных микросборках инверторы обозначаются буквами ЛН. Например, 1533ЛН1 содержится целых шесть инверторов. Зарубежные микросборки используют цифровое обозначение, например 74ALS04

Реализует операцию "И" - логическое умножение. В самом простом варианте на его вход подается два сигнала, на выходе получаем один сигнал. Если подается два нуля на выходе - ноль, две единицы - на выходе единица. Если на один вход поступает "1", а на другой ноль, то на выходе "0". Смотри рисунок с таблицей истинности для элемента И и его условно графическое изображение

Проще всего разобраться в работе логического элемента "И", при помощи упрощенной схемы, собранной на идеальных ключах с электронным управлением. В ней ток будет идти только тогда, когда оба ключа замкнуты, и поэтому, единичный сигнал на выходе будет только при обоих логических единицах на входе.

Третий основной логический элемент - это дизюнктор, выполняющий операцию ИЛИ - логическое сложение. Графическое изображение дизъюнктора показано в видеозаставке, чуть ниже.

Для наглядности представления представим Дизъюнктор "ИЛИ" в виде ключей. Но на этот раз соединим их параллельно. Как видно из рисунка ниже, уровень логической единицы установится на выходе, как только замкнется любой из ключей, подробней смотри в таблице истинности.

Рассмотрим реальный логический элементо на примере микросхемы транзисторно-транзисторной логики (ТТЛ) серии К155 с низкой степенью интеграции. На рисунке ниже, устаревшая, но все еще популярная микросборка К155ЛА3, содержащая четыре элемента 2И – НЕ. Кстати, с помощью ее можно собрать кучу .

По сути это уже знакомое нам изображение двух объединённых частей: элемента "2И" и "НЕ" на выходе. Таблица истинности для 2И-НЕ представлена ниже:

В результате на входе мы видим, что благодаря инвертору получается картина противоположная элементу «И». В отличие от трёх "0" и одной "1" мы видим три "1" и всего один ноль. Компонент цифровой логики «И – НЕ» часто называют элементом Шеффера.

Логический элемент 2ИЛИ – НЕ (а точнее целых четыре) имеется в микросборке К155ЛЕ1. Таблица истинности так же отличается от компонента "ИЛИ" инвертированием выходного сигнала.

На практике используются также двухвходовые элементы «исключающее ИЛИ. На рисунке ниже показано условное графическое обозначение элемента без инверсии и его таблица состояний. Главная функция данного компонента сводится к следующему, сигнал на выходе появится только тогда, если логические уровни на входах разные.

Рассмотрим практический пример «Исключающего ИЛИ» в схеме выделения фронта и среза импульса. В этой конструкции три компонента «Исключающий ИЛИ» применяются для задержки импульсов. DD1.4 - суммирующий. Выходные импульсы обладают стабильными фронтами и срезами. Длительность каждого выходного импульса равна утроенному времени задержки переключения каждого из 3-х компонентов. Временной интервал между фронтами выходных импульсов приблизительно равен длительности входного импульса. Кроме того, схема удваивает частоту входного сигнала.

Есть еще одно интересная функция «Исключающего ИЛИ». Если на один из входов подать постоянный «0», то сигнал на выходе компонента повторит входной сигнал, а если постоянный «0» поменять на постоянную «1», то выходной сигнал уже будет представлен инверсией входного.

Вот, реальный пример, отечественная микросборка К555ЛР4. Ее можно представить как 2-4И-2ИЛИ-НЕ:

Ее таблицу истинности не рассматриваем, так как цифровая микросборка не является базовым логическим элементом. Такие микросхемы часто выполняют специальные функции и бывают куда сложнее, чем рассмотренный пример.

Логическим элементом называется минимальная совокупность взаимосвязанных компонентов, выполняющая простейшие логические операции (действия) над входными сигналами. К таким операциям относятся, например, логическое сложение (элемент ИЛИ), логическое умножение (элемент И), инверсия или отрицание (элемент НЕ) и ряд других.

Описать работу логического элемента – это означает выбрать способ задания зависимости его выходного сигнала от входных сигналов. Другими словами – определить зависимость значений выходного сигнала от значений входных сигналов. Так как входные и выходные сигналы в логических (цифровых) устройствах могут принимать только два значения лог.0 и лог.1, то названные зависимости будут двоичными (и логическими).

Для отображения двоичных зависимостей можно использовать три основных способа табличный, графический и аналитический. Выбор способа зависит от цели описания элемента. Если требуется уяснить работу элемента в установившемся режиме (в статике), достаточно применить табличный способ – построить таблицу, указав в ней значения выходного сигнала при соответствующем наборе значений входных сигналов. Такие таблицы называют таблицами истинности, а наборы значений входных сигналов – комбинациями. Если элемент имеет несколько выходов (многофункциональный элемент), то в таблице истинности показывают соответствующее число столбцов со значениями выходных сигналов (функций).

Графическое описание работы (функционирования) элемента заключается в построении временных диаграмм, на которых отображаются в виде условных уровней (лог.1 и лог.0) значения входных и выходных сигналов и их последовательности. Этот способ применяют, когда необходимо рассмотреть работу элемента в динамике, то есть оценить его быстродействие либо определить минимальные и максимальные длительности входных и выходных сигналов и т.д.

Аналитический способ используют для анализа функциональных свойств элемента, поиска возможных вариантов его применения для построения более сложных логических устройств и для формализации условий его работы. Этот способ основан на использовании булевой алгебры, с помощью которой выходной сигнал (функция) представляется логической зависимостью от входных сигналов (аргументов функции). Принято функции обозначать прописными, а аргументы строчными буквами латинского алфавита. Логические операции над аргументами обозначают специальными символами. В технических приложениях булевой алгебры логическая сумма (дизъюнкция) обозначается знаком плюс «+», логическое произведение (конъюнкция) точкой, либо точка между переменными не ставится, либо используется символ &, а инверсия – чертой над переменной (ā) и читается «не а».

Чтобы исследовать (уяснить) функциональные свойства логического элемента, необходимо найти в явном виде алгебраическое выражение его выходной функции, отобразив зависимости логическими символами между входными переменными (аргументами). Затем, пользуясь законами и следствиями булевой алгебры, а также определениями дизъюнкции, конъюнкции и инверсии, сформулировать свойства элемента и определить его назначение.

Рассмотрим это на примере анализа свойств двухвходового логического элемента И-НЕ.

Условное графическое обозначение (УГО), таблица истинности и временные диаграммы работы этого элемента приведены на рис. 1.а и б и рис.1.в, соответственно.

Из УГО следует, что на входы потенциальные не инверсные, а выход – инверсный, потенциальный. Обозначим входные сигналы логическими переменными a и b, соответственно, по входам «вх.1» и «вх.2», а выходной сигнал функцией X.

Примем, что сигнал лог.1 отображается более высокими уровнем по отношению к сигналу лог.0 (такое соглашение называют соглашением «положительной логики» ). Тогда, проведя эксперимент, в котором на входы элемента будут подаваться все возможные наборы значений двух сигналов a и b (комбинации двоичного безызбыточного двухэлементного кода), можно определить значения выходного сигнала и построить таблицу истинности функции X , рис.1,б. Из анализа таблицы следует, что X принимает значение лог.0 только в единственном случае, когда оба входных сигнала одновременно принимают значение лог.1, т.е. когда сигналы лог.1 совпадают во времени. Поэтому выходной сигнал описывается инверсией логического произведения переменных a и b:

Таким образом, элемент И-НЕ (рис.1, а) представляет собой схему совпадения на два входа с инверсией выходного сигнала.

Рис.1 К анализу функциональных свойств элемента И-НЕ

Обратите внимание: функция X была определена по отношению к единичным значениям входных сигналов . Иными словами, если активными значениями входных сигналов считать лог.1, то элемент И-НЕ реализует инверсию логического произведения этих сигналов.

Если же за активное принять значение лог.0 (низкий уровень), то в то же самое время элемент И-НЕ реализует логическую сумму инверсий входных сигналов:

(2)

(2)

и ему будет соответствовать УГО рис.1,г. Это условное графическое обозначение элемента И-НЕ соответствует соглашения «отрицательной логики» .

Полученные выводы известны в булевой алгебре под названием «закона де Моргана относительно логического произведения»:

(3)

(3)

Анализируя выражение (1) и (2) при a=b, либо при а=1 или b=1, можно придти к выводу, что элемент И-НЕ можно использовать в качестве инвертора (элемента НЕ). Для этого на его оба входа надо подать один и тот же сигнал, либо один из входов подключить к шине лог.1, то есть подать сигнал логической единицы.

На рис. 2 приведены варианты реализации элемента НЕ на логическом элементе И-НЕ.

Рис. 2. Реализация элемента НЕ на элементе И-НЕ

Эти варианты являются следствиями закона тавтологии и закона дойного отрицания булевой алгебры:

Следует заметить, для микросхем ТТЛ неиспользование какого-либо входа (соответствующий вывод микросхемы не подключен ни к шине лог.0, ни к шине лог.1) равносильно подаче на этот вход сигнала лог.1.

Поэтому, если у многовходового элемента И-НЕ оставить входы «свободными», то на выходе будет всегда сигнал лог.0.

Кроме того, из выражения (1) следует, поскольку от перемены мест сомножителей произведение не меняется, то входы элементов И-НЕ логически равнозначны . Это означает, что безразлично, на какой вход будут подаваться входные сигналы, последние можно « менять местами».

Из булевой алгебры известно, инверсия логического произведения (называемая функцией Шеффера) образует базис, то есть полную систему логических функций. И, следовательно, состоящий только из логических элементов И-НЕ набор является функционально полным . В свою очередь, это означает, что на таком наборе можно построить любое цифровое устройство, какой сложности оно бы ни было.

Покажем, что только логическими двухвходовыми элементами И-НЕ (2И-НЕ) можно реализовать логическую сумму сигналов:

Допустим a= , b= и подставим эти значения в выражение (1):

Полученному соотношению соответствует функциональная схема, эквивалентная логическому элементу ИЛИ (см. рис.3,а и рис.3,б).

Реализовать просто логическое произведение (без инверсии) двух сигналов применением двух элементов И-НЕ, один из которых использовать как элемент НЕ, и включить их последовательно.

Таким образом, элементы 2И-НЕ позволяют реализовать три основные логические операции И, ИЛИ и НЕ, через которые представляется любая логическая функцию. Это доказывает функциональную полноту набора элементов И-НЕ.

Анализ работы элемента И-НЕ во времени проводят путем построения временных диаграмм при фиксированной последовательности входных сигналов (см. рис.1,в), показывая значения выходного сигнала в зависимости от значений входных. Так указанные диаграммы иллюстрируют случай, когда входные сигналы a и b изменяются в последовательности 00 -10 – 11 – 01 - 00.

Рис.3. Реализация логической суммы на элементах И-НЕ (а) и на элементе ИЛИ (б)

Причем длительности фронта и спада этих сигналов исчезающее малы, что показано скачкообразным изменением их уровней. Моменты изменения помечены, соответственно, t 0 и t 2 – для сигнала а, t 1 и t 3 – для сигнала b. Диаграмма сигнала X построена с учётом задержек в распространении сигналов от входов к выходу элемента, что отображено наклонными линиями фронта и спада выходного сигнала. Углом наклона отображают в некотором масштабе длительности переходов элемента из одного состояния в другое.

Временные диаграммы позволяют определить временные соотношения между входными и выходными сигналами и оценить быстродействие элемента, например, определить граничную частоту его переключения. Так из рассматриваемого примера диаграмм следует:

- ∆t 1 = t 2 – t 0 – длительность сигнала a;

- ∆t 2 = t 3 – t 1 – длительность сигнала b;

- (t 1 – t 0) – задержка сигнала b относительно фронта сигнала a;

- (t 2 – t 1) – длительность активного воздействия на элемент, когда оба входных сигнала имеют значение лог.1.

Если учесть задержки в изменении выходного сигнала относительно моментов (t 1 и t 2) изменения активного воздействия, то длительность сигнала X (значения лог.0) можно определить по формуле:

В формуле (5) знаки « - » и «+» обозначают арифметическое вычитание и сложение, соответственно, а t 10 зд.р. – задержка распространения сигнала при переходе элемента из состояния лог.1 в состояние лог.0 (при «включении»);

t 01 зд.р. – задержка распространения сигнала при переходе элемента из состояния лог.0 в состояние лог.1 (при «выключении»). Указанные задержки есть временные параметры логических элементов и их значения обычно приводятся в справочниках по ИМС .

Очевидно, если t 2 – t 1 < или = t 10 зд.р. , то выходной сигнал не изменит своего значения (лог.1) и элемент не будет реагировать на такие входные сигналы.

Аналогично можно построить временные диаграммы, когда исходное значение входных сигналов равно лог.1. И придти к выводу: элемент не будет реагировать на сигналы лог.0, если их длительность будет меньше или равна t 01 зд.р. . Обычно t 01 зд.р. >t 10 зд.р. , что обусловлено физикой работы базового логического элемента ИМС ТТЛ. Очевидно, что быстродействие элемента будет определяться граничной частотой переключения, которую можно определить по формуле

где косая соответствует символу арифметического деления.

3.Описание лабораторной установки

Данная лабораторная работа выполняется на субблоке «Логические элементы». На лицевой панели субблока расположены (см. функциональную схему рис.4):

· Тумблеры SA1 – SA4 для подачи сигналов лог.1 и лог.0 на входы исследуемых логических элементов;

· Светодиоды VH1 – VH4 для визуального контроля значений выходных сигналов;

· Гнёзда X1 – X17 для коммутации элементов между собой и подключения осциллографа.

Рис.4 Функциональная схема субблока «Логические элементы»

Для исследования элементов в динамическом режиме работы предусмотрен генератор импульсов прямоугольной формы D1 (несимметричный мультивибратор, собранный на элементах НЕ) и делитель частоты на двоично-десятичном счетчике импульсов D2 (микросхема К155ИЕ2).

Частоту генератора можно плавно регулировать в пределах от 20Гц до 2 кГц. Для этой цели на панель выведен движок переменного резистора. Частота импульсов на выходе 1 счётчика D2 (гнезда X2) в два раза, а на выходе 8 (гнезда X3) в десять раз меньше частоты генератора. На рис. 4,б приведены временные диаграммы сигналов на выходе генератора и выходах 1 и 8 счётчика, помеченные, соответственно, метками X1, X2 и X3. В работе исследуются логические элементы И, ИЛИ, И-НЕ и элемент НЕ, непосредственно представленные микросхемами: К155ЛИ1 (D3), K155ЛЛ1 (D4), K155 ЛА3 (D5) и К155ЛН1(D6)?, соответственно. Кроме того, можно исследовать схемы, эквивалентные логическим элементам ИЛИ-НЕ, ЗАПРЕТ, ИМПЛИКАТОР и др., реализуемые сборочными операциями на передней панели субблока.

4. Задание на лабораторную работу

4.1 Уяснить основные понятия и методы анализа функциональных свойств логических элементов.

4.2 Каждый логический элемент исследовать в статическом и динамическом режимах работы. При этом необходимо:

- Уяснить (составить) УГО элемента при соглашениях положительной и отрицательной логики;

- Составить таблицу истинности либо карту Карно функции, реализуемой рассматриваемым логическим элементом;

- Найти минимальное алгебраическое выражение функции;

- Построить временные диаграммы работы для характерных последовательностей входных сигналов;

- Сделать выводы о свойствах и применении элемента.

Перечень подлежащих обязательному анализу элементов приведен в табл. 4.1.

Дополнительно выполняется индивидуальное задание по исследованию многофункционального логического элемента (см. табл. 4.2.). Вариант указывается преподавателем либо выбирается по порядковому номеру бригады студентов.

4.3 Для микросхем серии К155 типов: ЛИ1, ЛЛ1, ЛН1 и ЛА3 привести электрические параметры, а также составить УГО этих микросхем, указав номера выводов (цоколёвку).

4.4 При выполнении работы руководствоваться методическими указаниями п.6.

Отчёт выполняется и оформляется в соответствии с требованиями, принятыми на кафедре АиКС. В отчёте представить:

5.1. УГО исследуемых логических элементов, таблицы истинности или карты Карно реализуемых ими функций. Данные оформить в таблице по форме табл. 4.1.

5.2. Временные диаграммы работы многофункционального логического элемента в динамическом режиме.

5.3. Выводы по функциональным свойствам и применению рассмотренных логических элементов.

Таблица 4.1

5.4. Условные графические обозначения и таблицу с основными электрическими параметрами, указанных в п.4.3 микросхем.

6. Методические указания

6.1. Перед включением напряжения питания поставьте тумблеры SA1,…SA4 (см. рис.4) в положение «ВЫКЛ.» (флажок вниз). Проконтролируйте подачу питания по загоранию соответствующего светодиода. Помните , на неподключенном входе логического элемента присутствует потенциал (2,4…3)В, равносильный сигналу лог.1. Убедитесь в исправности исследуемых элементов по светодиодам VH1,…VH4, включенным на выходы элементов. Соблюдайте правила безопасности! Запрещается соединять коммутационные гнёзда на выходах элементов с корпусом стенда либо с гнездом X15 (). Гнёзда X15 и X16 предназначены для подключения осциллографа (внешней его синхронизации).

Таблица 4.2

6.2. При выполнении задания руководствуйтесь методикой анализа, изложенной на примере анализа свойств элемента И-НЕ.

Наиболее просто зависимости выходных сигналов от входных задать с помощью карт Карно (матриц булевых функций). Ознакомиться с правилами построения карт Карно можно по . При анализе уясните однозначное соответствие между УГО элемента и реализуемой им функцией , то есть её алгебраическим выражением. Используйте это соответствие для адекватного перехода от функциональной схемы к логическому её описанию и обратно, от логического описания к функциональной схеме .

Поскольку в лабораторной установке используется ограниченное по номенклатуре число микросхем, то для исследования многофункциональных элементов (см. табл. 4.2) и даже элементов поз. 4, 6 и 7, табл.4.1 требуется предварительно составить их функциональные эквивалентные схемы. А затем, собрав схему на лицевой панели субблока, провести исследования.

Чтобы найти УГО элемента при соглашениях отрицательной логики, запишите алгебраическое выражение реализуемой им функции и примените к нему законы де Моргана. По полученному выражению составьте условное графическое обозначение. Правила формирования УГО легко уяснить, сопоставляя рис.1,а с выражением (1) и рис.1, г с выражением (2) для функции И-НЕ. Следуйте рекомендациям и требованиям ГОСТов .

6.3. Анализ работы логических элементов в динамическом режиме провести с учетом тех последовательностей сигналов, которые можно получить в лабораторной установке. При этом руководствуйтесь диаграммами, приведёнными на рис.4,б. Обратите внимание на соотношение длительностей импульсов (лог.0) и пауз (лог.1) сигнала X 1 . Эти соотношения следует выдерживать при построении диаграмм. Кроме того, длительности задержек t 10 зд.р. и t 01 зд.р. для микросхем К155 достаточно малы по сравнению с длительностями сигналов (составляют порядка десятков наносекунд), поэтому диаграммы допускается вычерчивать упрощенно, пренебрегая длительностями переходов. То есть переход от одного уровня к другому можно показывать скачком. Временные диаграммы в отчете можно привести только для многофункционального логического элемента согласно индивидуальному заданию по табл.4.2. Как видно, в табл.4.2 приведены трехвходовые элементы, у которых только два из трех входов логически равнозначны.

Эксперименты поставить для трех случаев, когда последовательности X 1 , X 2 и X 3 (см. рис. 4,б) меняются («местами») только на логически неравнозначных входах . В начале постройте диаграммы, а затем проведите эксперимент.

Определите по диаграммам временные параметры выходных последовательностей через параметры входных последовательностей для каждого из трех случаев. Под «параметрами» некоторой последовательности импульсных сигналов понимать: длительности импульсов и пауз; частоту следования импульсов (либо период их следования); длительность цикла изменения сигналов и др. Примите за единицу времени длительность одного такта ∆t, равного периоду следования импульсов с выхода генератора D1 (см. рис.4,а). Отобразите эти параметры на приводимых диаграммах.